台积电即将挑战极限:1nm工艺CPU预计会在2024年问世

人们如今应用的半导体材料绝大多数是硅基电源电路,面世早已六十年了,很多年来全是依照摩尔定律2年一次缩微的规律性发展趋势,但它终归是有極限的。台积电在提升5nm、3纳米及将来的2纳米以后,下一步就需要涉足1纳米加工工艺了。依据台积电的整体规划,2020年会批量生产5纳米工艺,2030年则会批量生产3nm加工工艺,2nm加工工艺早已在产品研发中了,预估会在2024年面世。

2纳米以后呢?台积电在此前的股东会上也表态发言,已经科学研究2nm下列的加工工艺,已经一步步靠近1nm加工工艺。

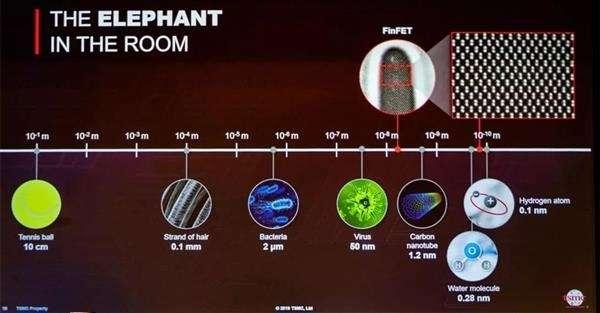

1nm加工工艺不仅是这一大数字看中关键,它也有很深的含意——1nm级別的加工工艺有可能是硅基半导体材料的结束,再往下沉就必须换原材料了,例如纳米技术片、碳纳米管这些,17年IBM榜首的科学研究团体就取得成功应用碳纳米管生产制造出了1nm三极管。

硅基半导体材料加工工艺的極限实际上一直在提升,以前的叫法中,10纳米、7纳米、5纳米、3纳米乃至2nm都被作为过硅基加工工艺的極限,如今看来還是一步步被提升了,如果不考虑到台积电、三星在加工工艺取名上的营销推广套路的话。

在今年的Hotchips大会上,台积电产品研发责任人、技术性科学研究总经理黄汉森(PhilipWong)在演说中就提到过半导体材料加工工艺極限的难题,他觉得来到2050年,三极管赶到氢原子限度,即0.1nm。

有关将来的关键技术,黄汉森觉得像碳纳米管(1.2纳米限度)、二维糜棱岩原材料等能够将三极管越来越更快、更迷你型;另外,改变运行内存(PRAM)、转动扭矩迁移随机存取运行内存(STT-RAM)待会立即和CPU封裝在一起,变小容积,加速数据信息传送速率;除此之外也有三d层叠封裝技术性。

稿源:TechTMT.Com

相关文章:

- AMD CPU产品线仍未放弃28nm挖掘机 抢占廉价Chromebook市场

- CPU大牛:Intel重整处理器研发流程 设计速度提升三倍

- Intel:CPU份额下降主要是产能不足 7nm工艺性能会追上来

- 外媒:台积电4月份开始大规模量产5nm芯片

- 华为希望90%国产软件可跑在鲲鹏CPU上 已适配2000多个产品

- 台积电将在美国设立全资子公司 注册资本35亿美元

- AMD锐龙R9-5900H移动处理器跑分曝光 媲美英特尔10核台式CPU

- 得益于苹果芯片订单 台积电的发展速度将领先于半导体行业

- 腾讯QQ“兴趣部落”即将全面停止运营并下线

- 台积电董事会批准在日本东京附近建立研发基地 将投1.86亿美元设立全资子公司

- AMD太过依赖台积电有弊端:产能掉链子致份额下滑

- Steam 8月硬件统计:AMD CPU显卡份额双降

- 随着硅成本的增加,CPU、GPU的价格可能会飙升

- 英特尔12代酷睿CPU成本降30% 自信成本优势将让对手无法复制

- 45W版12代酷睿CPU放开超频?Intel:仅有一款酷睿i9支持

- 英特尔CPU路线图更新:明年Meteor Lake 后年20A18A志强酷睿

- 如何选购CPU处理器?

- 如何选购CPU散热器?

- 打造M1同款芯片!Intel下一代CPU将用上台积电5nm工艺

- CPU温度过高有什么影响?